廣州白云反應(yīng)性離子刻蝕

硅材料刻蝕是集成電路制造過程中的關(guān)鍵步驟之一,對(duì)于實(shí)現(xiàn)高性能、高集成度的電路結(jié)構(gòu)具有重要意義。在集成電路制造中,硅材料刻蝕技術(shù)被普遍應(yīng)用于制備晶體管、電容器等元件的溝道、電極等結(jié)構(gòu)。這些結(jié)構(gòu)的尺寸和形狀對(duì)器件的性能具有重要影響。通過精確控制刻蝕深度和寬度,可以優(yōu)化器件的電氣性能,提高集成度和可靠性。此外,硅材料刻蝕技術(shù)還用于制備微小通道、精細(xì)圖案等復(fù)雜結(jié)構(gòu),為集成電路的微型化、集成化提供了有力支持。隨著半導(dǎo)體技術(shù)的不斷發(fā)展,硅材料刻蝕技術(shù)也在不斷創(chuàng)新和完善,如采用ICP刻蝕等新技術(shù),進(jìn)一步提高了刻蝕精度和加工效率,為集成電路的持續(xù)發(fā)展注入了新的活力。ICP刻蝕技術(shù)為微納制造提供了高效加工手段。廣州白云反應(yīng)性離子刻蝕

材料刻蝕是一種常見的制造工藝,用于制造微電子器件、光學(xué)元件等。然而,在刻蝕過程中,可能會(huì)出現(xiàn)一些缺陷,如表面不平整、邊緣不清晰、殘留物等,這些缺陷會(huì)影響器件的性能和可靠性。以下是幾種減少材料刻蝕中缺陷的方法:1.優(yōu)化刻蝕參數(shù):刻蝕參數(shù)包括刻蝕時(shí)間、溫度、氣體流量、功率等。通過優(yōu)化這些參數(shù),可以減少刻蝕過程中的缺陷。例如,適當(dāng)降低刻蝕速率可以減少表面不平整和邊緣不清晰。2.使用更高質(zhì)量的掩膜:掩膜是刻蝕過程中保護(hù)材料的一層膜。使用更高質(zhì)量的掩膜可以減少刻蝕過程中的殘留物和表面不平整。3.清洗和處理樣品表面:在刻蝕之前,對(duì)樣品表面進(jìn)行清洗和處理可以減少表面不平整和殘留物。例如,使用等離子體清洗可以去除表面的有機(jī)物和雜質(zhì)。4.使用更高級(jí)別的刻蝕設(shè)備:更高級(jí)別的刻蝕設(shè)備通常具有更高的精度和控制能力,可以減少刻蝕過程中的缺陷。5.優(yōu)化刻蝕模板設(shè)計(jì):刻蝕模板的設(shè)計(jì)可以影響刻蝕過程中的缺陷。通過優(yōu)化刻蝕模板的設(shè)計(jì),可以減少表面不平整和邊緣不清晰。浙江材料刻蝕版廠家Si材料刻蝕用于制造高性能的功率電子器件。

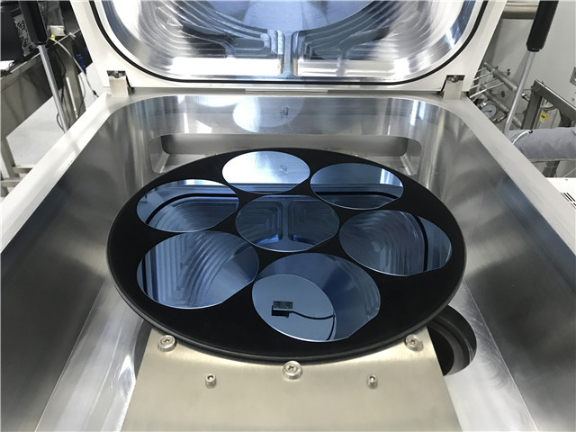

等離子刻蝕是將電磁能量(通常為射頻(RF))施加到含有化學(xué)反應(yīng)成分(如氟或氯)的氣體中實(shí)現(xiàn)。等離子會(huì)釋放帶正電的離子來(lái)撞擊晶圓以去除(刻蝕)材料,并和活性自由基產(chǎn)生化學(xué)反應(yīng),與刻蝕的材料反應(yīng)形成揮發(fā)性或非揮發(fā)性的殘留物。離子電荷會(huì)以垂直方向射入晶圓表面。這樣會(huì)形成近乎垂直的刻蝕形貌,這種形貌是現(xiàn)今密集封裝芯片設(shè)計(jì)中制作細(xì)微特征所必需的。一般而言,高蝕速率(在一定時(shí)間內(nèi)去除的材料量)都會(huì)受到歡迎。反應(yīng)離子刻蝕(RIE)的目標(biāo)是在物理刻蝕和化學(xué)刻蝕之間達(dá)到較佳平衡,使物理撞擊(刻蝕率)強(qiáng)度足以去除必要的材料,同時(shí)適當(dāng)?shù)幕瘜W(xué)反應(yīng)能形成易于排出的揮發(fā)性殘留物或在剩余物上形成保護(hù)性沉積(選擇比和形貌控制)。采用磁場(chǎng)增強(qiáng)的RIE工藝,通過增加離子密度而不增加離子能量(可能會(huì)損失晶圓)的方式,改進(jìn)了處理過程。當(dāng)需要處理多層薄膜時(shí),以及刻蝕中必須精確停在某個(gè)特定薄膜層而不對(duì)其造成損傷時(shí)。

材料刻蝕是一種通過化學(xué)反應(yīng)或物理作用將材料表面的一部分或全部去除的技術(shù)。它在許多領(lǐng)域都有廣泛的應(yīng)用,以下是其中一些主要的應(yīng)用:1.微電子制造:在微電子制造中,刻蝕被用于制造集成電路和微電子器件。通過刻蝕技術(shù),可以在硅片表面上制造出微小的結(jié)構(gòu)和電路,從而實(shí)現(xiàn)高度集成的電子設(shè)備。2.光學(xué)制造:在光學(xué)制造中,刻蝕被用于制造光學(xué)元件,如透鏡、棱鏡和濾光片等。通過刻蝕技術(shù),可以在光學(xué)元件表面上制造出精細(xì)的結(jié)構(gòu)和形狀,從而實(shí)現(xiàn)更高的光學(xué)性能。3.生物醫(yī)學(xué):在生物醫(yī)學(xué)中,刻蝕被用于制造微流控芯片和生物芯片等。通過刻蝕技術(shù),可以在芯片表面上制造出微小的通道和反應(yīng)室,從而實(shí)現(xiàn)對(duì)生物樣品的分析和檢測(cè)。4.納米技術(shù):在納米技術(shù)中,刻蝕被用于制造納米結(jié)構(gòu)和納米器件。通過刻蝕技術(shù),可以在材料表面上制造出納米級(jí)別的結(jié)構(gòu)和形狀,從而實(shí)現(xiàn)對(duì)材料性能的調(diào)控和優(yōu)化。總之,材料刻蝕是一種非常重要的制造技術(shù),它在許多領(lǐng)域都有廣泛的應(yīng)用。隨著科技的不斷發(fā)展,刻蝕技術(shù)也將不斷進(jìn)化和完善,為各行各業(yè)帶來(lái)更多的創(chuàng)新和發(fā)展機(jī)會(huì)。ICP刻蝕技術(shù)能夠?qū)崿F(xiàn)對(duì)多種材料的刻蝕。

MEMS(微機(jī)電系統(tǒng))材料刻蝕是制備高性能MEMS器件的關(guān)鍵步驟之一。然而,由于MEMS器件通常具有微小的尺寸和復(fù)雜的三維結(jié)構(gòu),其材料刻蝕過程面臨著諸多挑戰(zhàn),如精度控制、側(cè)壁垂直度保持、表面粗糙度降低等。ICP材料刻蝕技術(shù)以其高精度、高均勻性和高選擇比的特點(diǎn),為解決這些挑戰(zhàn)提供了有效方案。通過優(yōu)化等離子體參數(shù)和化學(xué)反應(yīng)條件,ICP刻蝕可以實(shí)現(xiàn)對(duì)MEMS材料(如硅、氮化硅等)的精確控制,制備出具有優(yōu)異性能的MEMS器件。此外,ICP刻蝕技術(shù)還能處理多種不同材料組合的MEMS結(jié)構(gòu),為器件的小型化、集成化和智能化提供了有力支持。感應(yīng)耦合等離子刻蝕在生物芯片制造中有重要應(yīng)用。深圳龍崗激光刻蝕

GaN材料刻蝕為高性能微波器件提供了有力支持。廣州白云反應(yīng)性離子刻蝕

硅材料刻蝕是半導(dǎo)體器件制造中的關(guān)鍵環(huán)節(jié)。硅作為半導(dǎo)體工業(yè)的基礎(chǔ)材料,其刻蝕質(zhì)量直接影響到器件的性能和可靠性。在硅材料刻蝕過程中,需要精確控制刻蝕深度、側(cè)壁角度和表面粗糙度等參數(shù),以滿足器件設(shè)計(jì)的要求。為了實(shí)現(xiàn)這一目標(biāo),通常采用先進(jìn)的刻蝕技術(shù)和設(shè)備,如ICP刻蝕機(jī)、反應(yīng)離子刻蝕機(jī)等。這些設(shè)備通過精確控制等離子體或離子束的參數(shù),可以實(shí)現(xiàn)對(duì)硅材料的高精度、高均勻性和高選擇比刻蝕。此外,在硅材料刻蝕過程中,還需要選擇合適的刻蝕氣體和工藝條件,以優(yōu)化刻蝕效果和降低成本。隨著半導(dǎo)體技術(shù)的不斷發(fā)展,硅材料刻蝕技術(shù)也在不斷創(chuàng)新和完善,為半導(dǎo)體器件的制造提供了有力支持。廣州白云反應(yīng)性離子刻蝕

- 數(shù)字光刻廠商 2025-06-19

- 廣州花都刻蝕 2025-06-19

- 北京激光刻蝕 2025-06-19

- 蕪湖ICP刻蝕 2025-06-19

- 低線寬光刻 2025-06-19

- 甘肅光刻代工 2025-06-19

- 甘肅深硅刻蝕材料刻蝕 2025-06-19

- 廣東真空鍍膜廠家 2025-06-19

- 廣州白云反應(yīng)性離子刻蝕 2025-06-18

- 廣州刻蝕炭材料 2025-06-18

- 錫山區(qū)優(yōu)勢(shì)充電樁銷售客服電話 2025-06-19

- 中國(guó)澳門模塊化光譜儀海洋光學(xué)網(wǎng)站 2025-06-19

- 陜西熱電偶哪里有采購(gòu) 2025-06-19

- 廣州精密芯片哪家好 2025-06-19

- 探針socket現(xiàn)價(jià) 2025-06-19

- 金華PA66防水接頭定制 2025-06-19

- 廣州HA-003重載連接器聯(lián)系人 2025-06-19

- 上海懸掛式LED透明屏價(jià)錢 2025-06-19

- 中國(guó)香港IGBT模塊誠(chéng)信合作 2025-06-19

- 湖北機(jī)頂盒紅外線接收頭1838 2025-06-19