茂名SDIO協議分析儀廠家

我們會找到信號與上升的Vref值交叉的位置。如果Vref升至足夠高,信號的頂部軌跡將通過Vref,我們便會看到眼的頂端。再將Vref升高一點會導致Vcomp保持在Vlo,表示信號不會升至該電之,將Vref移至零以下會看到眼的下半部。eyescan/eyefinder顯示窗口會在每個信號的eyescan圖下方顯示eyefinder交疊部分,以此顯示eyefinder與eyescan之間的這一關系。通過在eyescan圖中將Vth水平線向上和向下移動,可以獲得距離眼中心該偏移量位置處的eyefinder視圖。無論用戶界面中的閾值如何設置,邏輯分析儀的差分輸入將始終應用于接收器。這意味著可通過將電壓閾值手動設置為非零值允許在差分對中使用公共模式電壓。如果信號擺幅中心與地線差距于100mV,eyescan將自動執行此操作。邏輯分析儀的觸發設置邏輯分析儀觸發非常困難,而且還需花費量時間。假設如果知道如何編程,則應該可以毫不費力地設置邏輯分析儀觸發。然而,這是不可能的,因為許多概念對邏輯分析來說都是的。本節的目的就是介紹這些主要概念及如何有效地使用它們。傳送帶類比:我們可以將邏輯分析儀的內存比作一條很長的傳送帶,而從被測設備(DUT)獲取的樣本就像是傳送帶上的箱子。新的箱子被放置在傳送帶一端。訓練器哪里買?找歐奧!茂名SDIO協議分析儀廠家

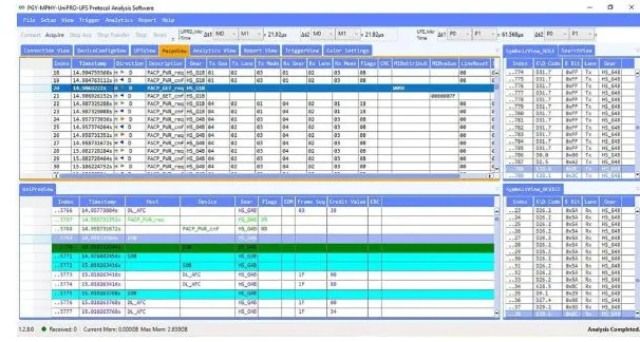

USBtypeC等高速協議抓取和分析的服務。序列步驟存儲總會覆蓋默認存儲,但只針對序列步驟存儲中特別指定的條件。處理默認存儲和序列步驟存儲之間的時一定要謹慎。雖然設置邏輯分析儀很困難,但觸發函數可以降低此過程的難度。觸發函數是可以組合起來設置觸發的常用構建塊。由于這些函數涵蓋了多數普通觸發,因此通過選擇適當的函數并將其填充到數據中即可設置觸發。下圖顯示了邏輯分析儀觸發用戶界面。請注意,觸發函數位于屏幕左側的一個醒目位置。圖21使用觸發函數通常,設置復雜觸發的難題是對問題進行分解。換句話說,就是如何將復雜觸發映射到序列步驟、分支和布爾邏輯表達式。將問題分解為不同時發生的事件。這些事件對應于序列步驟。掃描觸發函數列表,嘗試找出一些與步驟1中確定的事件相匹配的函數。將所有剩余事件分解為布爾邏輯表達式及其相應操作。各個布爾邏輯表達式/操作對分別對應于序列步驟中的一個單獨分支。請記住,可能存在只用于為序列步驟處理存儲限定的“存儲”分支。設置邏輯分析儀觸發與編寫軟件相徑庭。如果使用預定義的觸發函數和較早編寫的文檔完善的觸發來完成其他工作,就可降低設置邏輯分析儀觸發的難度。在沒有其他可用的資源時。連云港SD協議分析儀電話協議分析儀就找歐奧電子。

歐奧電子是Prodigy在中國區的官方授權合作伙伴,ProdigyMPHY,UniPro,UFS總線協議分析儀測試解決方案不會收到EAR進出口方面的管制。同時還有代理其他總類的協議分析儀,包括嵌入式設備用的SDIO協議分析儀,QSPI協議分析儀及訓練器,I3C協議分析儀及訓練器,RFFE協議分析儀及訓練器等等。我司還有代理SPMI協議分析儀及訓練器,車載以太網分析儀,以及各種相關的基于示波器的解碼軟件和SI測試軟件。同時,歐奧電子也有提供高難度焊接,以及高速信號,如UFS,DDR3/DDR4,USBtypeC等高速協議抓取和分析的服務。DampedResistorProbing),電阻匹配探測(ResistiveDividerProbing)。短線探測會增加電容負載。舉例:探頭電容負載是,連接短線是50歐姆微帶線。C=3pF/in),長度1英寸。則整個探頭的電容負載是,這個短線是電容負載的主要部分。被測系統可容忍的負載電容是多少呢?需要參考被測電路的系統上升時間,一般規則:短線的電氣長度<>PCB傳輸延遲:150ps/in系統上升時間:500ps則電氣長度:則短線長度:(100ps)/(150ps/in)=。如果沒法減小短線長度,可以試著用阻尼電阻探測的方式。阻尼電阻有2個作用:隔離來自短線的電容,消減來自短線的反射。

整體功能雖然不能和專業儀器相比,但是用較低的成本來實現特定的功能,也是非常成功的設計。本文以下討論的邏輯分析儀,主要是指這類入門級設計。基于電腦并口的邏輯分析儀曾是主流,但是近年來電腦系統逐步不再配置并口,這類設計已經成為明日黃花,還具有原理學習的價值。另一類的邏輯分析儀,是以低速單片機為基礎的。很多愛好者用PIC、AVR等常見單片機設計了自己的作品。但這類單片機邏輯分析儀的共同弱點就是采樣速度太慢,通常不超過1MHz。以USBIO芯片為基礎的入門級邏輯分析儀現在為流行。比如Saleaelogic,還有類似的USBee等。這類產品主要采用一個USBIO芯片,例如CYPRESS公司的CY7C68013A-56PVXC,所有的信號觸發和處理工作都是電腦上的軟件完成的,硬件部分就只是一個數據記錄儀。高采樣速度為24MHz。它們可以“無限數量”地采樣,因為所有的數據都是存儲在電腦里的。目前一般多是8個通道,更多的通道數量會成比例地降低高采樣速度。這類產品構造簡單,方便易用,價格便宜,是調試單片機開發工作的好工具。它的缺點主要是采樣速度只有24MHz、8個通道,對于分析高速并行總線就不能勝任了。更進一步的設計,需要增加FPGA、SRAM等器件。UART協議分析儀/訓練器找歐奧!

沒有額外的被測設備)的一小段時間內,可以自動:定位每個通道上的建立/保持窗口。針對盡可能寬的數據有效窗口調整閾電壓設置。眼定位是獲得盡可能小的邏輯分析儀建立/保持窗口的一種簡單方法。眼定位概要:對于指定的狀態采樣時鐘,眼定位可在時鐘沿前后的一個固定時間范圍內查找數據信號轉變(閾電壓交叉點),并為顯示相關內容以幫助設置佳采樣位置。為了了解眼定位顯示,需為每個活動時鐘沿拍攝一張有關該時鐘沿的數據信號轉變的“照片”。將此照片看作快照、定格畫面或頻閃觀測儀(位于時鐘沿中心或與時鐘沿同步)。到達時鐘沿的時間為T=0。例如,如果選擇盒1上時鐘輸入的上升沿作為狀態采樣時鐘,每次拍攝“照片”時,都將達到盒1時鐘上的上升沿。盒1時鐘沿之間的時間是否相同無關緊要。如果同時在上升沿和下降沿上進行采樣,那么在每一個時鐘沿上都會拍攝一張“照片”。此外,在活動沿之間消耗了多少時間也不重要。每一個時鐘沿上都要拍攝“照片”。要構建眼定位顯示,需要將無數張這樣的“照片”堆疊在彼此的頂端。每張“照片”都在T=0時對齊,此時將達到活動時鐘沿。照片拍自上升沿還是下降沿并沒有關系;它們會在T=0時對齊。構建顯示后。100BaseTl (Automotive)邏輯分析儀/訓練器找歐奧!清遠SDIO協議分析儀售價

邏輯訓練器廠家哪家好?歐奧電子!茂名SDIO協議分析儀廠家

您應使用示波器。2、邏輯分析儀的特點是:a)能夠同時觀察多個信號;b)能夠查看硬件系統的系統信號;c)能夠按高低電平模式觸發多條信號線,并查看結果。邏輯分析儀與示波器的工作方式相似:用水平軸數據的時間,垂直軸數據的電壓幅度。雖然,邏輯分析儀沒有示波器那么高的電壓分辨率和事件間隔精確度,但是邏輯分析儀能夠同時捕獲并顯示多個信號,示波器卻做不到。當系統中的信號穿越閾值時,邏輯分析儀和您的邏輯電路具有相同的反應。所以在查看總線(微處理器的地址、數據或控制總線)的時間關系時,邏輯分析儀特別有用,它可以對微處理器總線信息解碼更有意義,更直觀的方式表示信息。當您的電路通過了參量設計階段后,對許多信號的定時關系感興趣,并且要在高低電平模式上觸發時,那么邏輯分析儀就是極好的選擇。五、邏輯分析儀的功能如前所述,絕大多數邏輯分析儀是兩種儀器的合成,部分是定時分析儀,第二部分是狀態分析儀。1.定時分析定時分析是邏輯分析儀中類似示波器的部分,它與示波器顯示信息的方式相同,水平軸時間,垂直軸電壓幅度。定時分析首先對輸入波形的采樣,然后使用用戶定義的電壓閾值,確定信號的高低電平。定時分析只能確定波形是高還是低。茂名SDIO協議分析儀廠家

- 珠海EMMC協議分析儀找哪家 2025-06-14

- 惠州UART邏輯分析儀找哪家 2025-06-13

- 連云港USB分析儀品牌 2025-06-13

- 汕尾UFS協議分析儀廠家 2025-06-13

- 南通RFFE協議分析儀售價 2025-06-13

- 揭陽UART邏輯分析儀品牌 2025-06-13

- 湛江I2C/SPI協議分析儀那家好 2025-06-13

- 南通UART邏輯分析儀費用 2025-06-13

- 株洲PCIE協議分析儀電話 2025-06-13

- 嘉興EMMC邏輯分析儀售價 2025-06-13

- 閩清熱電偶共同合作 2025-06-14

- 有哪些液相色譜儀哪家強 2025-06-14

- X熒光礦物多元素含量檢測儀 2025-06-14

- 智能水分測定儀哪個好 2025-06-14

- 徐匯區本地通訊設備工廠直銷 2025-06-14

- 浙江省永康市電源類地磅配件供應 2025-06-14

- 河南在線塵埃粒子檢測系統 2025-06-14

- 重慶智能型低噪音壓力平衡單座調節閥 2025-06-14

- 高精度PH計有幾種 2025-06-14

- 商砼水分測定儀多少錢 2025-06-14